# A Battery-Balancing Nine-Level Inverter

# R. Dharmaprakash<sup>1</sup>, P. Vetri velavan<sup>2</sup>

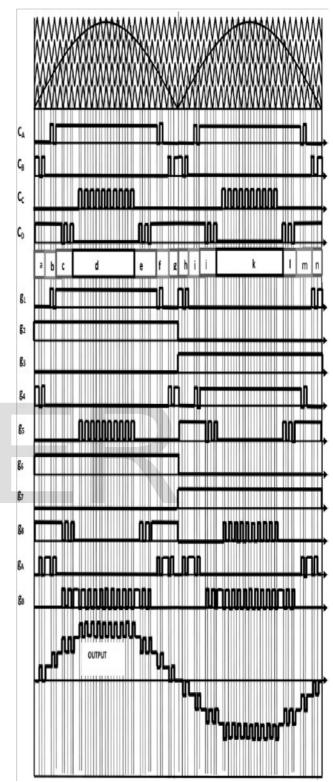

Abstract—In this paper, a nine-level inverter was designed and implemented to operate a battery balanced discharge system, which increases the ability of a stored energy utilization of a renewable energy sources. Also in this system a cascaded multilevel inverter with selective harmonic elimination and an algorithm to calculate the switching angles of a cascaded multilevel inverter minimizing the total harmonics distortion (THD) is proposed. The input of each level of cascaded multilevel inverter circuit is directly connected to a battery. Duty cycle of switch of each level is controlled to contain the ac output voltage with minimize total harmonic distortion. Additionally, the battery balanced discharged function is also achieved. Finally, an equivalent model block diagram of the proposed system to verify the feasibility and advantage by using Simulink software MATLAB. The stimulation results show that the proposed multilevel inverter with selective harmonic elimination and battery-balanced discharge function can eliminate harmonic and improve the cascaded batteryimbalanced problem effectively as we required.

Index Terms—Cascaded Inverter, Minimum THD, Battery balanced discharge.

#### **I.INTRODUCTION**

In recent years, environmental concern and continuous depletion of fossil fuel reserves have spurred significant interest in renewable energy sources. The energy storage became a dominant factor in economic development with the widespread introduction of renewable sources. Unlike other common energy storage in prior use such as wood or coal, electricity must be used as it is being generated, or converted immediately into another form of energy such as potential, kinetic or chemical. Until recently electrical energy has not been converted and stored on a major scale, however new efforts to that effect began in the 21st century. An early solution to the problem of storing energy for electrical purposes was the development of the battery as an electrochemical storage device.

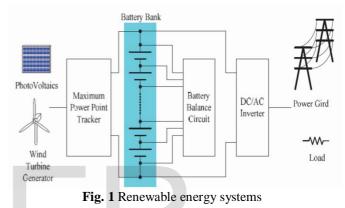

However, renewable energy sources such as wind turbine generators and photo- voltaic are intermittent in nature, and produce fluctuating active power. Interconnecting these intermittent sources to the utility grid at a large scale may affect the voltage/frequency control of the grid, and may lead to severe power quality issues. An energy storage system is indispensable for compensation which is a large capacity of the battery bank. In order to reduce energy loss in transmission lines and increase the overall battery capacity, the battery bank is usually connected in series for high voltage DC power supply. Batteries have previously been of limited use in electric power systems due to their relatively small capacity and high cost. However, since about the middle of the first decade of the 21st century, newer battery technologies have

#### 1. R. Dharmaprakash

JNTU University **2.P. Vetri velavan,** M.E Research scholar

St. Peter's University

been developed that can now provide significant utility scale load-leveling capabilities some of which, as of 2013, showed promise of being competitive with alternative methods.

A similar possible solution to deal with the intermittency issue of solar and wind energy is found in the capacity. This result is smaller storage capacity and shorter cycle life. Therefore, the power conversion system requires a battery balancing circuit as shown in fig.1, to adjust each battery voltage to be equal.

The battery balancing strategies can be categorized into three approaches:

- 1. Balancing by providing additional charging current for each battery until the voltage of each unit reaches a set threshold. But this process is either the battery subjected to over charged condition or the switching device is subjected to high voltage stress.

- 2. OBalancing by individually draining excessive current from battery which voltage is above a set threshold back to the main charging bus. This process needs the high voltage conversion ratio of converter, which will cause

the system efficiency decrease and the high voltage stress on the switching devices.

3. Balancing by allowing the current to flow both in and out off the batteries until the voltage of each reaches a set threshold. This process is uses the switching circuit of control the battery energy, which transfers the high capacity battery energy into the low capacity battery by a capacitor or a inductor storage of energy temporarily. It will increase the energy loss in transmission lines and switch components.

However, an additional battery balancing circuit not only increase circuit complex and cost .but also reducing efficiency. To solve this problem, a cascaded multilevel inverter with selective harmonic elimination and batterybalancing discharge function is proposed. Multilevel cascade converters are an attractive topology for mediumvoltage high power applications. Since it is simple and modular in structure, and can reach medium/high voltages with low voltage/current harmonics without using step-up transformers or switching devices connected in series. In this paper, the input of each level of cascaded multilevel inverter circuit is directly connected to a battery. The duty cycle of each level is controlled to contain the ac output voltage with minimize total harmonic distortion. Additionally, the batterybalancing discharge function is also achieved. Finally, a prototype is realized to verify the feasibility and excellent performance.

### **II.MULTI-LEVEL INVERTER**

A multilevel inverter is more recent and popular type of power electronic converter that synthesizes a desired output voltage from nine levels of dc voltages as inputs. If sufficient number of dc sources is used, a nearly sinusoidal voltage waveform can be synthesized. In comparison with the hardswitched two-level pulse width modulation inverter, multilevel inverter offers several advantages such as, its capabilities to operate at high voltage with lower dv/dt per switching, high efficiency and low electromagnetic interference [1]-[4].

To synthesize multilevel output ac voltage using different levels of dc inputs, semiconductor devices must be switched on and off in such a way that desired fundamental is obtained with minimum harmonic distortion. The commonly available switching technique is selective harmonic elimination (SHE) method at fundamental frequency, for which transcendental equations characterizing harmonics are solved to compute switching angles [2], [3]. It is difficult to solve the SHE equations as these are highly nonlinear in nature and may produce simple, multiple, or even no solutions for a particular value of modulation index.

A big task is how to get all possible solution sets where they, exist using simple and less computationally complex method. Once these solution sets are obtained, the solutions having least THD are chosen. In [4]-[6], iterative numerical techniques have been implemented to solve the SHE equations producing only one solution set, and even for this a proper initial guess and starting value of modulation index for which solutions exist are required. In [7], [8], theory of resultants of polynomials and the theory of symmetric polynomials has been suggested to solve the polynomial equations.

A difficulty with these approaches is that for several Hbridges connected in series, the order of the polynomials become very high thereby making the computations of the solutions of these polynomials very complex. Optimization technique based on Genetic Algorithm (GA) was proposed for computing switching angles for 9-level inverter in [9].

The implementation of this approach requires proper selection of certain parameters such as population size, mutation rate etc, thereby its implementation becomes also difficult for higher level inverters. To circumvent above problems, in this paper the application of the NewtonRaphson method for solving these equations is proposed. The proposed technique is implemented in such a way that all possible solutions for any number of H-bridges connected in series are computed for any arbitrary initial guess with negligible computational effort. A complete analysis for an 9-level inverter using four H-bridges per phase in series is presented, and it is shown that for a range of modulation index, switching angles can be computed to produce the desired fundamental voltage V1 = (s 4Vdc/) while eliminating 5<sup>th</sup>,7<sup>th</sup>, 11<sup>th</sup> and 13<sup>th</sup> harmonic components.

#### **Cascade Multilevel Inverter**

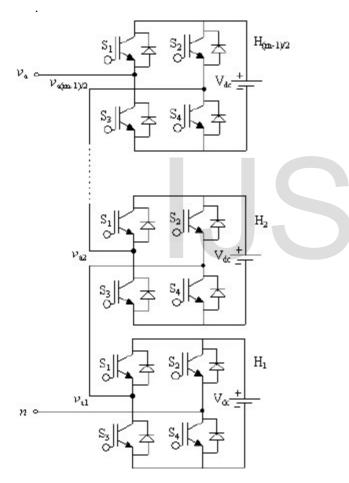

Cascade Multilevel Inverter (CMLI) is one of the most important topology in the family of multilevel and multipulse inverters. It requires least number of components with compare to diode-clamped and flying capacitors type multilevel inverters and no specially designed transformer is needed as compared to multi-pulse inverter. It has modular structure with simple switching strategy and occupies less space [1], [3]. The CMLI consists of a number of H-bridge inverter units with separate dc source for each unit and is connected in cascade or series as shown in Fig. 2. Each Hbridge can produce three different voltage levels: +Vdc, 0, and –Vdc by connecting the dc source to ac output side by different combinations of the four switches S1, S2, S3, and S4.

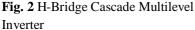

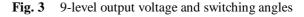

The ac output of each H-bridge is connected in series such that the synthesized output voltage waveform is the sum of all of the individual H-bridge outputs. By connecting the sufficient number of H-bridges in cascade and using proper modulation scheme, a nearly sinusoidal output voltage waveform can be synthesized. The number of levels in the output phase voltage is 2s+1, where s is the number of Hbridges used per phase. Fig. 3 shows a 9-level output phase voltage waveform using four H-bridges. The magnitude of the ac output phase voltage is given by *van=va1+va2+va3+va4*[2].

#### III. PWM

Multicarrier phase disposition PWM scheme is employed in the generation of the gating signals. Basic principle of the proposed switching strategy is to generate gate signals by comparing the rectified sinusoidal modulating/reference signal, at the fundamental frequency, with four triangular carrier waves having higher switching frequency and inphase but different offset voltages. In practice, carrier to

| $v_{o}$<br>$V_{S}$<br>$2V_{S}$<br>$3V_{S}$<br>$4V_{S}$<br>0<br>$-V_{S}$<br>$-2V_{S}$<br>$-3V_{S}$<br>$-4V_{S}$ | S <sub>1</sub><br>off<br>on<br>on<br>off<br>off<br>off<br>off | S <sub>2</sub><br>on<br>on<br>on<br>off<br>off<br>off                                           | S <sub>3</sub><br>off<br>off<br>off<br>off<br>off<br>on<br>on<br>on          | S4<br>off<br>off<br>off<br>off<br>off<br>off<br>on<br>off<br>on<br>on | S₅<br>off<br>off<br>off<br>off<br>off<br>off<br>off |                      | Sen on on offffffffffff                       | S7<br>off<br>off<br>off<br>off<br>off<br>off<br>on<br>on<br>on | Se<br>of<br>of<br>of<br>of<br>of<br>of<br>of | f of<br>f of<br>f of<br>f of<br>f of<br>f of<br>f of<br>f of | S <sub>A</sub><br>on<br>off<br>off<br>off<br>off<br>off<br>off | S <sub>B</sub><br>Off<br>Off<br>Off<br>off<br>off<br>off<br>off<br>off |

|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------|----------------------|-----------------------------------------------|----------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------|

| Range of M <sub>a</sub>                                                                                        | θ <sub>1</sub>                                                | $\theta_2$                                                                                      | θ                                                                            | θι                                                                    | θ                                                   | θ                    | θ                                             | θ                                                              | θ                                            | θ <sub>10</sub>                                              | θ <sub>11</sub>                                                | θ <sub>12</sub>                                                        |

| M <sub>a</sub> <0.25<br>0.25 < M <sub>a</sub> ≤0.5<br>0.5 < M <sub>a</sub> ≤0.75<br>M <sub>a</sub> >0.75       | (z2)<br>sin^1(AJAm)<br>sin^1(AJAm)<br>sin^1(AJAm)             | (#2)<br>(#2)<br>sin <sup>-1</sup> (AJA <sub>#</sub> )<br>sin <sup>-1</sup> (2AJA <sub>#</sub> ) | (#2)<br>(#2)<br>(#2)<br>sin <sup>-1</sup> (3A <sub>0</sub> /A <sub>m</sub> ) | 172)<br>1721<br>1723<br>1733                                          | (π2)<br>(π2)<br>π-θ <sub>2</sub>                    | (#2)<br>1-0-<br>1-0- | (3π2)<br>Π+θ <sub>1</sub><br>π+θ <sub>1</sub> | (3π2)<br>(3π2)<br>π+θ2<br>π+θ2                                 | (3:12)<br>(3:12)<br>(3:12)<br>(3:12)         | (3#2)<br>(3#2)<br>(3#2)<br>2#-03                             | 3.π2 <br> 3.π2 <br>2π-θ2<br>2π-θ2                              | (3t/2)<br>2x - 0<br>2x - 0<br>2x - 0                                   |

Table 2 Range of modulation index and the corresponding values of the phase angle displacement

International Journal of Scientific & Engineering Research, Volume 5, Issue 4, April-2014 ISSN 2229-5518

fundamental frequency ratio of 40 is adopted for better performance of this multilevel PWM scheme [10]. For one cycle of the fundamental frequency, the proposed multilevel inverter operates through eight modes. Fig. 3 illustrates the per unit output voltage waveform for one cycle. The eight modes are described as follows

$\begin{array}{l} Mode \ 1 := 0 \ , \ vt \le u1 \ and \ u6 \le vt \le p; \\ Mode \ 2 := u1 \le vt \le u2 \ and \ u5 \le vt \le u6 \\ Mode \ 3 := u2 \ , \ vt \le u3 \ and \ u4 \le vt \le u5; \\ Mode \ 3 := u3 \le vt \le u4 \\ Mode \ 5 := p \ , \ vt \le u7 \ and \ u12 \le vt \le 2p; \\ Mode \ 6 := u7 \le vt \le u8 \ and \ u11 \le vt \le u12 \\ Mode \ 7 := u8 \ , \ vt \le u9 \ and \ u10 \le vt \le u11; \\ Mode \ 8 := u9 \le vt \le u10 \\ \end{array}$

The phase angle  $\theta,$  depends on the modulation index, Ma[11]

#### **IV.SELECTIVE HARMONIC ELIMINATION**

There are many popular methods are used to reduce the harmonics in order to get an effective results. The popular methods for high switching frequency are Sinusoidal PWM and Space Vector PWM. For low switching frequency methods are space vector modulation and selective harmonic elimination. The SPWM technique has disadvantage that it cannot completely eliminate the low order harmonics. Due to this it cause loss and high filter requirement is needed. In Space Vector Modulation technique cannot be applied for

unbalanced DC voltages.

**Fig. 5** System block diagram

SHE PWM technique uses many mathematical methods to eliminate specific harmonics such as 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup>, and 13<sup>th</sup> harmonics. The popular Selective Harmonic Elimination method is also called fundamental switching frequency based on harmonic elimination Theory. As shown in Fig.3, a multilevel converter can produce a quarter-wave symmetric

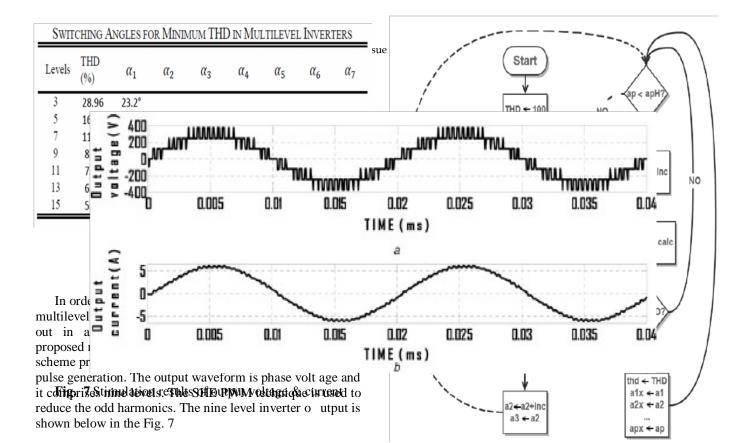

stepped voltage waveform synthesized by several DC voltages. Multilevel inverters provide a less THD than other inverters and it can improve with more levels added. One of the drawbacks is the calculation of the switching angles since the more levels are needed, more angles must be calculated and more time is spent in calculation. Fig. 3 shows a multilevel inverter output for nine steps. Multilevel inverters provide a less THD than other inverters and it can improve with more levels added. One of the drawbacks is the calculation of the switching angles since the more levels are needed, more angles must be calculated and more time is spent in calculation. Fig. 3 shows a multilevel inverter output for nine steps. One of the most used techniques for finding the switching angles is to use the rms of harmonic each battery output voltage components and the switching voltage components coefficients to eliminate some harmonics. The number of harmonics to be eliminated is equal to the number of switching angles to be calculated minus one, with this technique A computer program can be used to find the switching angles for the minimum THD using the same equation, nevertheless the amount of time of calculation increases with the number of angles. Calculation of THD requires computing of p cosines, two square roots, 2psummations, p+2 multiplications, and one division, where p is the number of angles to be calculated. Calculation of the minimum THD depends on angle resolution. For one degree resolution the first angle goes from 1° to 89° in steps of 1°, the second angle goes from  $2^{\circ}$  to  $89^{\circ}$  and so on, so that for p angles it is needed (90-n)/p1 where p1 in the range of 1 to p THD calculations. checks for the minimum THD in all possible values o∏ f each

For example, for two angles with one degree resolution it is needed 3,916 THD calculations, assuming the program

angle. For three angles with the same resolution it is needed 113,564 THD calculations. The flowchart of the program is shown in Fig. 6. The more switching angles are needed, the more for loops must be nested and the program can spent a lot of time running. That is why the increment (Inc) is a key to find first a close value for switching angles and then modify the limit values of each loop, that is, angle i that goes from aiL to aiH, its limit values. The increment (Inc) starts with a large value, say 6 in the all range of the angles, from 0 to 90 degrees.

The first run of the program gives the seeds or close angle values for the minimum THD. For example, for p=5 and Inc= 6 the first run of the program gives 7°, 14°, 27°, 40° and 59°. This first run needs 2002 THD calculations, less than is needed for two angles calculation. The new limit values can be calculated from the Inc value as aiL= aix-Inc/2 and aiH= aix+Inc/2, where aix is the new value of the angle i. For this example the limit values are (4, 10), (11, 17), (24, 30), (37, 43) and (56, 62). Closer angles for the real minimum THD can be found with Inc equal to 1. In this case the second run of the program gives 6°, 17°, 29°, 42° and 60°, and the new limit values for Inc equal to 0.1 are (5.5, 6.5), (16.5, 17.5), (28.5, 29.5), (41.5, 42.5) and (59.5, 60.5).

The second run of the program needs 7,776 THD calculations. The third run of the program with these values gives the angles in table 3 for three to fifteen levels.

IJS

# VI.CONCLUSION

Presented in this paper is a new configuration for cascaded multilevel inverter. The operational principles, modulation scheme and switching functions have been analyzed in detail. The proposed multilevel inverter exhibited the behaviors of 3-, 5- and 7-level inverters earlier reported, in addition to the characteristics herein. By controlling the modulation index, the desired number of levels of the inverter's output voltage has been achieved.

Fig.6 Flow chart for switching angle calculation

In this project, a cascaded multilevel inverter with selective harmonic elimination and battery-balanced discharge function is succeeding proposed. The input of each level of cascaded multilevel inverter circuit is directly connected to a battery. Duty cycle of switch of each level is controlled to contain the ac output voltage with minimize total harmonic distortion. The simulation system results show that the proposed multilevel inverter with selective harmonic elimination and battery-balanced discharge function can harmonic and the eliminate improve cascaded batteryimbalanced problem effectively as we wanted.

## REFERENCES

- Jih-Sheng Lai, Fang Zheng Peng, "Multilevel Converters-A New Breed of Power Converters", IEEE Trans. on Industry Applications, vol. 32, no. 3, pp. 509-517, May/June 1996.

- [2] Fang Zheng Peng, Jih-Sheng Lai, et al, "A Multilevel Voltage-Source Inverter with Separate DC Sources for Static Var Generation", IEEE Trans. on Industry Applications, vol. 32, no. 5, pp. 1130-1138, September/October 1996.

- [3] Jose Rodriguez, J S Lai, and F. Z. Peng, "Multilevel Inverters: A Survey of Topologies, Controls, and Applications", IEEE Trans. on Industrial Electronics, vol. 49, no. 4, pp. 724-738, August 2002.

- F. Z. Peng, J. W. McKeever, and D. J. Adams, "Cascade Multilevel Inverters for Utility Applications", IECON Proceedings (Industrial Electronics Conference), vol. 2, pp. 437-442, 1997.

- [5] L. M. Tolbert, F. Z. Peng, and T.G. Habetler, "Multilevel converters for large electric drives", IEEE Transactions on Industry Applications, vol. 35, no. 1, pp. 36-44, Jan. /Feb. 1999.

- [6] R. Lund, M.D. Manjrekar, P. Steimer, T.A. Lipo, "Control strategies for a hybrid seven-level inverter", in Proceedings of the European Power Electronic Conference, Lausanne, Switzerland, September 1990.

- [7] John N. Chiasson, Leon M. Tolbert, Keith J. McKenzie,

Zhong Du, "Control of a Multilevel Converter Using Resultant Theory", IEEE Transaction on Control Systems Technology, vol. 11, no. 3, pp. 345-353, May 2003.

- [8] John N. Chiasson, Leon M. Tolbert, Keith J. McKenzie, Zhong Du, "A new approach to solving the harmonic elimination equations for a multilevel converter", in Proc. IEEE Industry Applications Soc. Annu. Meeting, Salt Lake City, UT, pp. 640-645, Oct.12-16, 2003.

- [9] Burak Ozpineci, Leon M. Tolbert, John N. Chiasson,

"Harmonic Optimization of Multilevel Converters Using Genetic Algorithms", IEEE Power Electronics Letters, vol. 3, no. 3, pp.92-95, September 2005.

- [10] Grahame Holmes, D., Lipo, T.A.: 'Pulse width modulation for power converters, principles and practice' (John Wiley and Sons, Inc., Publication, USA, 2003)

- [11] Lezana, P., Rodriguez, J., Oyarzun, J.A.: 'Cascaded multilevel inverter with regeneration capability and reduced number of switches', IEEE Trans. Ind. Electron., 2008, 55, (3), pp. 1059–1066.

- [12] J. Rodriguez, J. S. Lai, and F. Z. Peng, "Multilevel Inverters: a Survey of Topologies, Controls, and Applications," IEEE Transactions on Industrial Electronics, vol. 49, August 2001, pp. 724–737.

- [13] Y. Liu, H. Hong, and A. Q. Huang, "Real- Time Calculation of Switching Angles Minimizing THD for Multilevel Inverters with Step Modulation," IEEE Transactions on Industrial Electronics, Vol. 56, No. 2, February 2009, pp.

285–293.

- [14] J. N. Chiasson, L. M. Tolbert, K. J. McKenzie, and Z. Du, "Elimination of Harmonics in a Multilevel Converter Using the Theory of Symmetric Polynomials and Resultants," IEEE Transactions on Control Systems Technology, Vol. 13, No. 2, March 2005, pp. 216- 223.

- [15] H. Taghizadeh and M. T. Hagh, "Harmonic Elimination of Cascade Multilevel Inverters with Nonequal DC Sources Using Particle Swarm Optimization," IEEE Transactions on Industrial Electronics, Vol. 57. No. 11, November 2010, pp. 3678- 3684.

- [16] S. G. Song, F. S. Kang, and S. Park, "Cascaded Multilevel Inverter Employing Three- Phase Transformers and Single DC Input," IEEE Transactions on Industrial Electronics, Vol. 56, No. 6, June 2009, pp. 2005- 2014.

- [17] N. Yousefpoor, S. H. Fathi, N. Farokhnia, and H. A. Abyaneh, "THD Minimization Applied Directly on the Line- to . Line Voltage of Multilevel Inverters", IEEE Transactions on Industrial Electronics, Vol. 59, No. 1, January 2012, pp. 373- 380.

[18] Y. Sahali and M. K. Fellah, "Application of the Optimal Minimization of the Total Harmonic Distortion technique to the Multilevel Symmetrical Inverters and Study of its Performance in Comparison with the Selective Harmonic

Elimination Technique", Speedam 2006, International

Symposium on Power Electronics, Electrical Drives, Automation and Motion, May 2006, pp. 1342-1348.

- [19] J. Li, Y. Liu, S. Bhattacharya, and A. Q. Huang, "An Optimum PWM Strategy for 5- Level Active NPC (ANPC)

Converter Based on Real- Time Solution for THD Minimization", Energy Conversion Congress and Exposition, September 2009, pp. 1976- 1982.

- [20] D. Zhong, L. M. Tolbert, J. N. Chiasson, and B. Ozpineci, "A Cascade Multilevel Inverter Using a Single DC Source", Applied Power Electronics Conference and Exposition, March 2006.

- [21] MATLAB Version 7.2.0.232 (R2006a).